Robot obserwujący linię

Budowa robota dla początkujących. Opis i lista materiałów: https://gitlab.com/kozik/obserwujacy-linie/

z- 3

- #

- #

- #

- #

- #

- #

Budowa robota dla początkujących. Opis i lista materiałów: https://gitlab.com/kozik/obserwujacy-linie/

z

Kompilacja startów rakiet z Festiwalu Meteor 2021. Pustynia Błędowska 4.09.2021

z

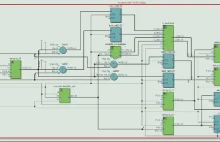

Środowisko Quartus pozwala na sprawdzenie w jaki sposób nasz projekt został zrealizowany w układzie FPGA. W tym krótkim wpisie pokażę jak to można sprawdzić.

zChyba każdy zna kultową grę PONG. Jest ona z nami już od niemal 50 lat. Dzisiaj stworzymy własną wersję! Napiszemy ją w języku SystemVerilog i uruchomimy na układzie FPGA Max10 produkcji firmy Intel.

z![VGA - Intel FPGA Max10 Eksperymenty #14 [PL]](https://wykop.pl/cdn/c3397993/link_1618861399nqX57vTdSfRu50nT7yWnRO,w220h142.jpg)

Dzisiaj podłączymy do płytki Rysino monitor. Użyjemy złącza VGA. Do generowania sygnału posłużą nam 3 1-bitowe przetworniki DAC. W filmie znajdziemy: 0:00 Wprowadzenie 0:16 Podłączenie sprzętu 2:17 Programowanie 2:47 Prezentację działania Do wykonania przykładu potrzebne będą: * płytka...

z

Pierwszy odcinek kursu SystemVerilog. Dowiemy się co to za język i do czego jest używany. Napiszemy także nasz pierwszy projekt i przeprowadzimy jego symulację w programie ModelSim.

z![Wyświetlacz 7-segmentowy - VHDL na Rysino #04 [PL]](https://wykop.pl/cdn/c3397993/link_1604507369MKNYwk0sHpIq2KmOvOW9f7,w220h142.jpg)

Dowiemy się jak działa wyświetlacz 7-segmentowy. Opiszemy w języku VHDL jego sterownik. Następnie dołączymy go do wyjścia licznika z poprzedniego eksperymentu.

z

Podstawy VHDL - języka opisu sprzętu. Tym razem połączymy ze sobą dwa liczniki, a następnie zobaczymy jak nasz projekt został zrealizowany z wykorzystaniem wewnętrznych bloków układu FPGA. Na koniec demonstracja w sprzęcie ;)

z![Licznik modulo N - VHDL na Rysino #02 [PL]](https://wykop.pl/cdn/c3397993/link_1603524845znuN2QCL6RpOL7HjWGldsK,w220h142.jpg)

Drugim projektem jest licznik modulo N. Stworzymy parametryzowalny moduł z asynchronicznym resetem i wejściem ce (clock enable). Na wyjściu dostępny będzie stan licznika oraz informacja o przepełnieniu ov (overflow). W filmie znajdziemy: 0:00 Intro 0:18 Syntezowalny moduł w VHDL 5:10...

z![Bramki logiczna - VHDL na Rysino #01 [PL]](https://wykop.pl/cdn/c3397993/link_16033970416ee3HOPr8flOjnKkNuYpxr,w220h142.jpg)

Witam w pierwszym odcinku VHDL na Rysino. Pierwszym projektem, dzięki któremu zapoznamy się z językiem będa bramki logiczne: OR i AND. Zaimplementujemy kod syntezowalny i testy. Następnie uruchomimy symulację i przeprowadzimy syntezę projektu. Końcowy efekt sprawdzimy w sprzęcie. W...

z

LFSR, czyli rejestr przesuwny z liniowym sprzężeniem zwrotnym jest często używany do obliczenia cyklicznej sumy kontrolnej (CRC). Zbudujemy więc moduł oblicz...

z

Dzisiaj zajmiemy się rejestrem przesuwnym. najpierw zbudujemy prostszą, jednokierunkową wersję. Zarówno dane jaki i sygnał zegarowy będziemy wymuszać za pomo...

z

Dzisiaj zbudujemy licznik modulo dziesięć. Będzie on zliczał liczbę naciśnięć przycisku podłączonego do wejścia układu FPGA. Po drodze napotkamy problem z dr...

z

W dzisiejszym odcinku #FPGAgraficznie stworzymy licznik zliczający w górę i w dół. Stan 8 najstarszych bitów wyświetlimy na diodach LED, a kierunek zliczania...

z

Dzisiaj przyglądniemy się wewnętrznej budowie układów FPGA. Jako przykład posłuży znamy nam już z poprzednich części Intel Max10. Jak zobaczymy mimo dość pow...

z

Dzisiaj zapoznamy się z narzędziem Signal Tap. Pozwala ono na obserwacje sygnałów z wnętrza układu FPGA. W tutorialu skorzystamy z projektu z poprzedniego fi...

z

Tutorial pokazuje w jak w środowisku graficznym programu Quartus II zamodelować przerzutnik typu D. Następnie przeprowadzona zostaje symulacja jego działania...

z

Tutorial pokazuje w jaki sposób stworzyć swój pierwszy projekt w środowisku graficznym dostępnym w programie Quartus. Stworzymy nasz pierwszy projekt: bramki...

z

Making-of z procesu powstawania układu elektronicznego w warunkach domowych. Trawienie płytki, lutowanie i prezentacja działania klawiatury do wpisywania emot ikonek...

zRocznica

od 06.03.2022

Wykop.pl

Tak samo możesz sprawdzić, czy mnożenia są wykonane w logice czy blokach DSP. Albo czy wszystkie rejestry w bloku DSP są użyte, co ma wpływ na maksymalną częstotliwość pracy.

Także